Antmicro

@antmicro

Antmicro is a software-driven tech company developing open and modern industrial edge and cloud AI systems.

The scalable Audio Latency Tester for developing AR/XR systems is easily embeddable into more complex measuring and testing setups involving both audio & video. Use it with a PC or an embedded platform like our open Jetson Orin Baseboard: antmicro.com/blog/2025/05/s… @NVIDIAEmbedded

Learn about the recent improvements in our openEMS-driven Signal Integrity simulation flow, featuring adaptive discretization, differential pairs and updated @Blender visualizations with CI-friendly, command line pipelines: antmicro.com/blog/2025/07/r…

We’re excited to launch AutoML for Embedded, an open-source tool co-developed by ADI and @antmicro that simplifies building and deploying machine learning models on edge devices. Explore the tool and start building smarter at the edge: bit.ly/3IkUAi7

By combining SAIF wave format support in Verilator with the @OpenROAD_EDA toolchain, we provide a flexible, open source-driven solution for analyzing signal activity and optimizing power efficiency in digital design: antmicro.com/blog/2025/07/p… @Google @CHIPSAlliance

Thanks to our collaboration with @adi_news, you can now use AutoML in Kenning to quickly find and deploy optimized models for ultra low-power devices with AI accelerators. Read about the improvements that enabled support for MAX78002 CNN accelerator in Kenning and @ZephyrIoT:…

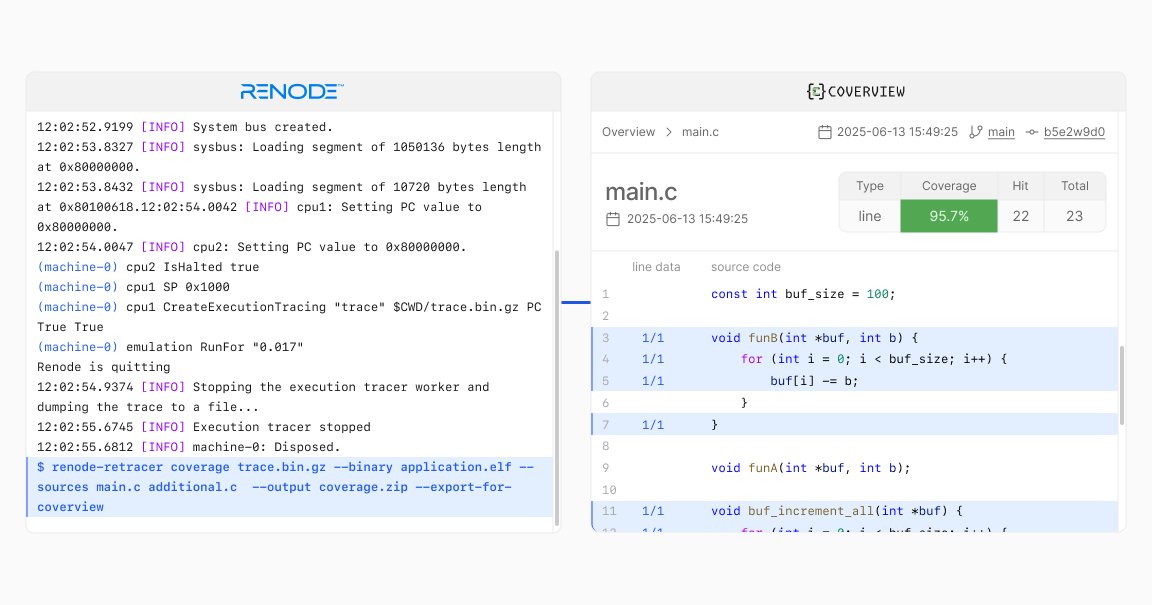

Using @renodeio's extensive execution tracing capabilities and the new integration with Coverview you can now track code coverage, without additional instrumentation of the code, and aggregate results into a unified, interactive dashboard: antmicro.com/blog/2025/06/r…

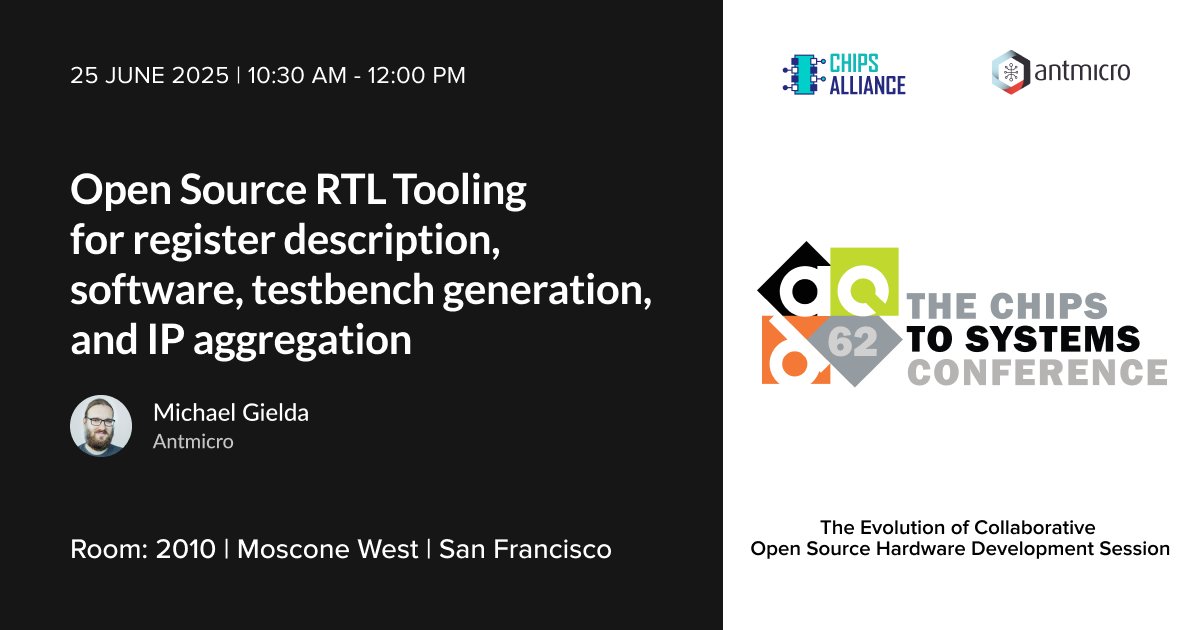

At this year's @DAC_Conference we will demonstrate how SystemRDL combined with open source tools such as OpenTitan's testplanner and uvmdvgen, and Antmicro's Topwrap SoC aggregation & Pipeline Manager can be used to maintain a coherent system state and ensure effective…

Find out how we enhanced Verilator's hierarchical mode for better performance and scalability & join us at @DACconference to learn more about this and other recent improvements we introduced to Verilator: antmicro.com/blog/2025/05/i… @CHIPSAlliance

What does a collaborative open source chip design environment look like? At DAC, CHIPS Alliance’s Robert Mains moderates a session on open ISAs, PDKs, EDA, cloud-based design, & Caliptra. 📅 June 25 | ⏰ 10:30am 🔗 hubs.la/Q03rWpqL0 #DAC2025 #CHIPSAlliance #OpenHardware

Join us at @DACconference for the BoF Open Source EDA Session to learn about latest updates in Verilator for architectural exploration, verification, and testing: improved hierarchical mode, measuring coverage, SAIF support and more. …urce-eda-birds-of-a-feather.github.io @chipsalliance

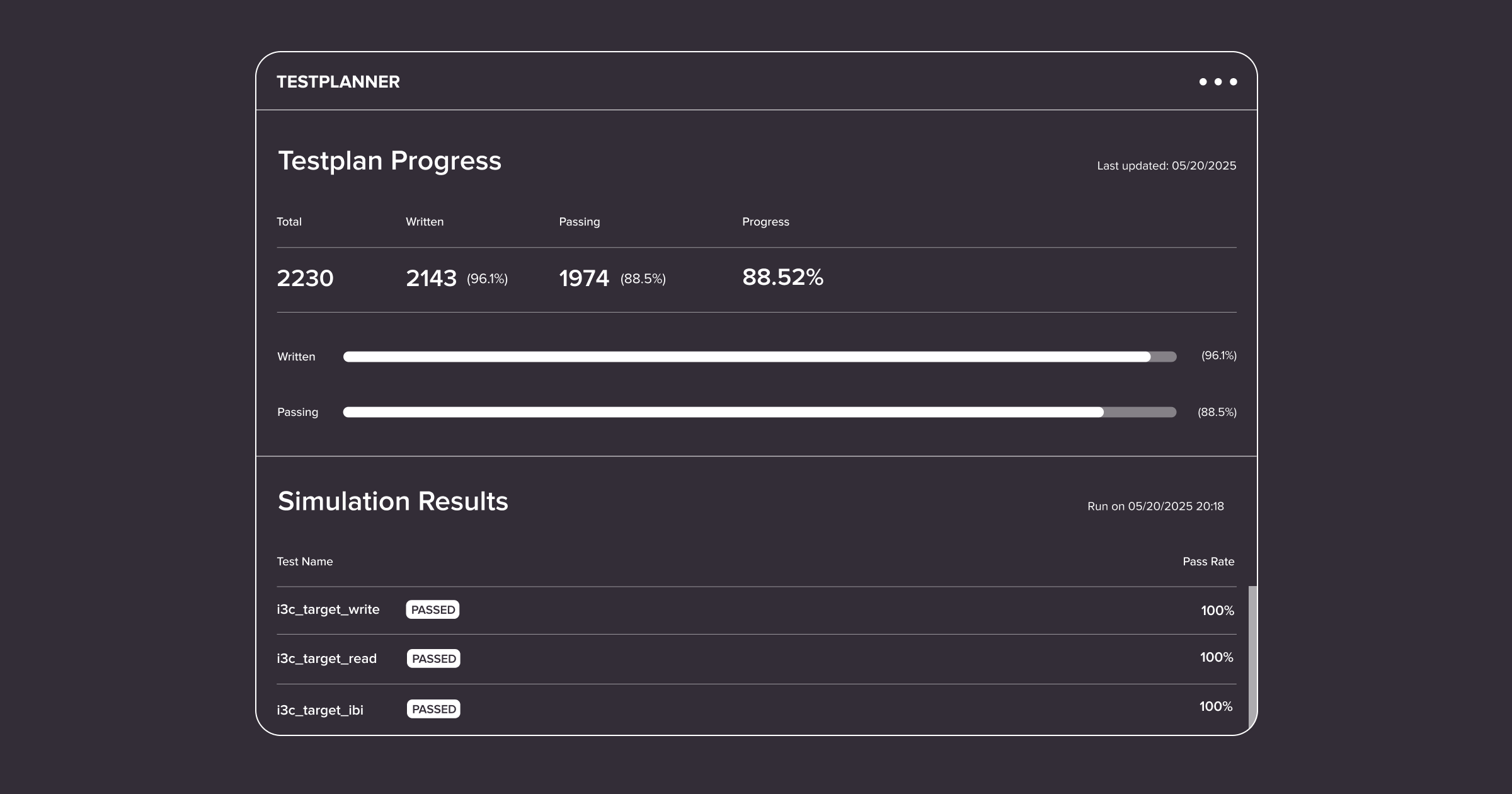

We released a standalone, enhanced version of @lowRISC OpenTitan's testplanner with test result interlinking and more for improved digital design & DV tracking. Generate testplans & simulation result tables, explore our @CHIPSAlliance I3C project example: antmicro.com/blog/2025/06/a…

New Blog: Interactive #RTL Coverage Dashboards for #VeeR and #Caliptra. In this post, @antmicro walks through how Coverview is used to track verification for the VeeR EL2 core, part of the Caliptra project. chipsalliance.org/news/coverage-…

We improved #Verilator's hierarchical mode in terms of verilation and compilation times, resource usage and scalability to enable faster-turnaround ASIC design flows for complex designs. See how we can extend Verilator for your use case: antmicro.com/blog/2025/05/i… @CHIPSAlliance

New revision of Antmicro's highly popular Open Source Jetson Orin Baseboard is back in stock at @CircuitHub. Same small footprint with support for both @Nvidia Jetson Orin Nano and NX SoMs in Super mode for an extra edge AI compute boost order.openhardware.antmicro.com

We extended @Google Pigweed SDK to support Bluetooth on @Arm Cortex-M33 @NXP MIMXRT595 MCU for use in constrained wireless devices. Check out the PoC using 1x MIMXRT595 MCU runing Pigweed and 3x @NordicTweets nRF52840 SoCs with @ZephyrIoT and @renodeio antmicro.com/blog/2025/05/p…

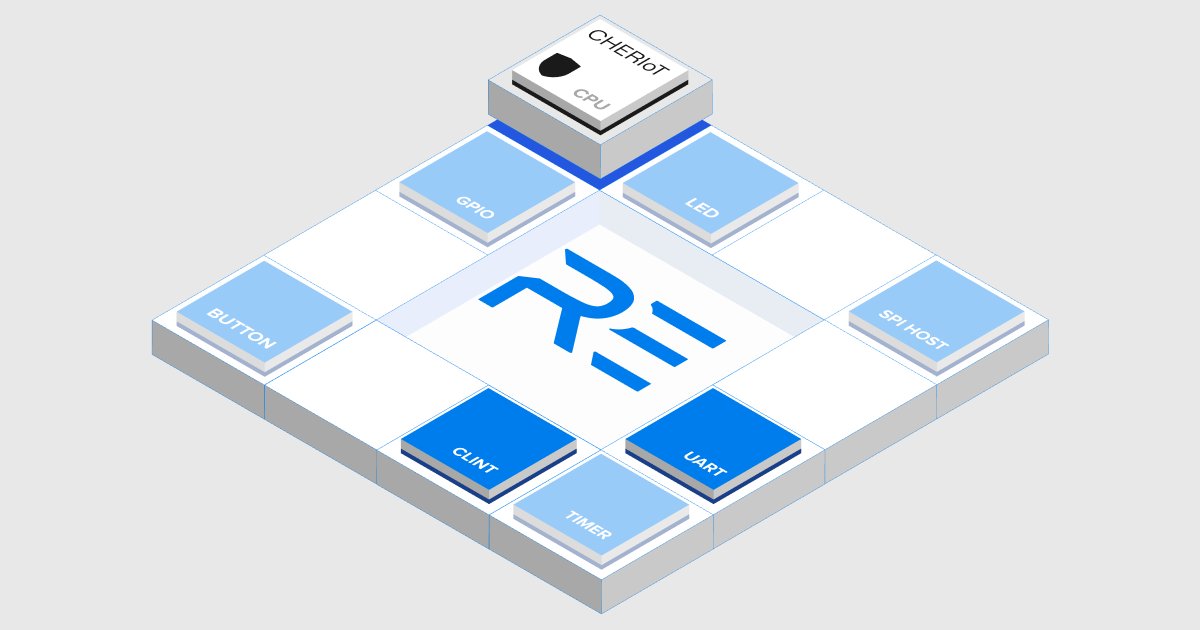

See how you can benefit from full-system simulation of CHERI-enabled hardware in @renodeio thanks to its integration with MPACT-Cheriot, and try a co-simulation demo of a complete CHERI-based @risc_v platform: antmicro.com/blog/2025/05/r… @Google

Discover how we improved @renodeio's performance on 64-bit @Arm-based machines such as @Apple Macs, @Raspberry_Pi and server infrastructure with native 64-bit Arm host support, now available for both macOS and Linux: antmicro.com/blog/2025/05/n…

Watch our RISC-V in Space talk on using Renode to create digital twins of platforms, run unmodified SW in multi-node heterogeneous systems, debug in a fully controlled environment and test rigorously end to end youtube.com/watch?v=xFaI39… @antmicro @risc_v @gaisler_space @esa