Ryuji Fuchikami

@Ryuz88

超リアルタイムコンピューティングを目指して、ソフト/FPGA/基板設計、オリジナルのAI(微分可能回路によるLUT-Net)まで手広くやってる福岡在住のプログラマです。自営業者(フリーランス)になりました。 各種成果物は GitHub などからどうぞ。http://github.com/ryuz

LUT-NetというFPGAのLUTを直接学習させる独自手法で、MNISTのSemanticSegmentationに挑戦した動画です。 外部メモリレスで低遅延で低リソース動くため、OLEDがまるでガラスのように見えますが、ちゃんとAIで数字を認識して色を付けています。 ryuz.txt-nifty.com/blog/2020/03/p…

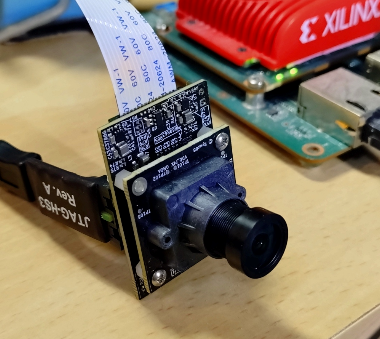

外部に相応のFPGAを用意すれば KV260 の MIPIコネクタで理屈上は2.5Gbps x 2 = 5Gbps ができる。 KR260 の SLVS-EC コネクタで理屈上 12.5Gbps x 2 = 25Gbps ができる。 のでここに拡張治具を作るのはあるかもしれない。 Artix-UltraScale+ 安くならないかな。

どなたが ffmpeg が AI あれば最強の CLI ツールになると言われてましたが、今日体感しました。 下手に OpenCV で動画作るより、一度連番静止画でpng 出力してから ffmepg に頼む方がいろいろできる。

I released Verylup 0.1.7, the official installer for Veryl. This release includes the following features: * `no-self-update` option/feature support Please see the release blog for the detailed information: veryl-lang.org/blog/annoucing…

はてなブログに投稿しました GOWINで加算の性能を調べてみる - Ryuz's tech blog ryuz.hatenablog.com/entry/2025/07/… #はてなブログ

なかなかこの先どこまでちゃんと動かせるか読めませんが、3連休で頑張って進めたので、妄想ページをアップデートしました。 rtc-lab.com/products/rtcl-…

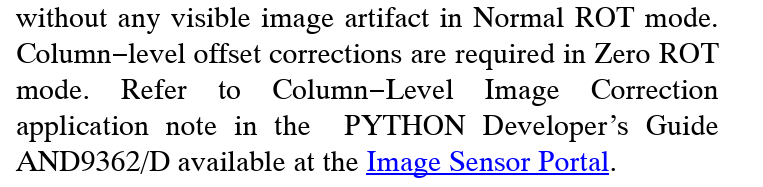

しかし今更ながら黒レベルおかしいよなと言うのと、レンズキャップしてても明るい&揺らいでるなので、レジスタ設定ならいいけど電源回路周りで何かやらかしてるような気もしていて怖いな。

なお、 1280x1024 の PYTHON1300 と レジスタ仕様が共通なので、設定的にはこのサイズまで設定できてしまう模様。 そしてサイズを超えた部分は黒が出てくるようだ。

どうやら オンセミの Image Sensor Portal なるところにアクセスするには、NDAが必要なようだ。 よし、もう絵は出てるしNDA無しでやれるところまでやってみようw onsemi.jp/download/data-…

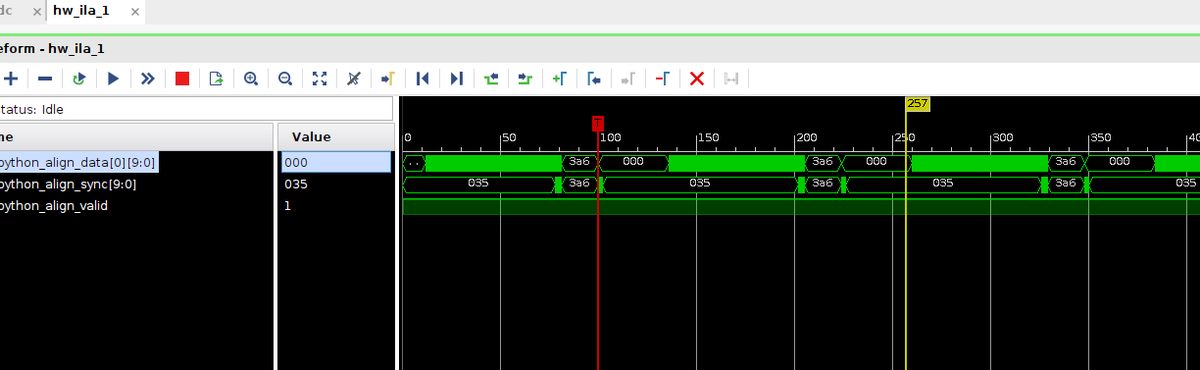

PYTHON300センサー、ZROTモードにして xsm_delay を小さくしていくと、フレームレートが上がっていくけど左側から黒くなっていくという面白い動きをする。 そして真っ黒(0x00)かと思ったら強い明りのあるラインはなんか写っている!

私が昔作ったITRON仕様のRTOSのネーミングを頭文字がHOSになるようにしたのもそうですし、ゆうきまさみ先生の漫画が私に与えた影響は大きいですね(笑)。

join したいというか元々そこで誰よりも大きなことをやらかした自覚はあるので、むしろこっちかもw jp.quora.com/watashi-wo-tsu…

KiCadのファイルをGit管理しているときに、コミット間の差分を可視化するツールを作っています。主に自分で使うために作り始めたのですが、割と良い感じになってきました。類似の他のツールとは異なり、KiCadの標準機能を活用し、追加で必要なライブラリがとても少なくなっています。