ロン | 半導体VTuber

@Semicon_Academy

✨ YouTube『Semicon Academy』 / 2022.3.31~ ✨ 半導体VTuber / 25.6.13~ ✨ 技術・業界動向・雑学 ✨ V個人勢・モデル自作 配信 #セミコンライブ / 毎週水曜は #半導体クイズ

【 LINEスタンプ販売のお知らせ 】 Semicon Academyから、『半導体スタンプ』をリリースしました✨✨ 職場でもプライベートでも使える(?)スタンプが16種類!! ぜひご活用下さい🔥🔥 [半導体スタンプ] line.me/S/sticker/2412…

![Semicon_Academy's tweet image. 【 LINEスタンプ販売のお知らせ 】

Semicon Academyから、『半導体スタンプ』をリリースしました✨✨

職場でもプライベートでも使える(?)スタンプが16種類!!

ぜひご活用下さい🔥🔥

[半導体スタンプ]

line.me/S/sticker/2412…](https://pbs.twimg.com/media/F4Xyzk9aUAAjblE.jpg)

ご存じの通りサムスンは3nm製品の歩留まりの向上に苦戦中。 サムスンを50%、TSMCを90%とすると、ウェハから得られるチップ数の倍近い差になる。 ただしウェハ単価は工場によります。 TSMCにはGoogleやAMD、Qualcommと需要が集中しており、市場価格は歩留りの差を完全には反映しない可能性があります

サムスンがテスラのAI向けチップ『AI6』の製造に向け約2兆4000億円の契約。 テスラは製造先を分散しており、AI5についてはTSMC、台湾・アリゾナで製造、AI6はサムスン、テキサスとなる予定。 地政学リスクと関税を意識した動きか

Samsung’s giant new Texas fab will be dedicated to making Tesla’s next-generation AI6 chip. The strategic importance of this is hard to overstate. Samsung currently makes AI4. TSMC will make AI5, which just finished design, initially in Taiwan and then Arizona.

半導体チップでは基本的に長期動作・低故障率が要求されます。 例えば車のECUに一台あたり100以上のチップが搭載されると仮定し、完成品で100万台に1台の故障率を目指す場合、各チップの許容される不良率は0.00001%以下でなければなりません。 特に人命を預かる車載・航空・医療ではより厳格です

半導体技術者不足、人材派遣会社にはビジネス拡大の好機…TSMC進出をきっかけに九州に相次ぐ育成施設(読売新聞オンライン) #Yahooニュース news.yahoo.co.jp/articles/6a170…

パネルレベルパッケージでは、基板サイズが従来の縮小ステッパーのレチクルサイズ(26×33mm)に比べて遥かに大きいため、従来のフォトマスクによる露光では対応が困難です。 そのためダイシフトや深い焦点深度に対応した専用のステッパーの他、レーザーによる直接描画技術(LDI)の採用も進んでいます

またTSMCは、AIのロジックとHBM需要に対応するため、2027年までに9.5インチ(≒24cm)レチクルサイズのCoWoSを開始します。 レチクルサイズが大きいほどパッケージできるHBM数が増えるようです @Vengineer 氏のブログ参照 vengineer.hatenablog.com/entry/2024/05/…

Intelが24日の決算説明会で、14Aノードで大口顧客を獲得できない、また技術開発がマイルストーンを達成できなかった場合、開発を減速、中止する可能性を示した。 14Aの開発費用は数十億ドル規模になるとされ、投資の前に実現性や需要を確認することは極めて妥当だと思います tomshardware.com/tech-industry/…

STMicroelectronicsがNXP SemiconductorsのMEMS事業を9~9.5億米ドルで買収!NXPのMEMS事業の売上は約3億米ドル。2社のMEMS事業の売上を足せば約9億米ドル。MEMSセンサーの売上でSTはTDKを抜かして2位に返り咲く。コンシューマー向けが得意なSTと車載センサーに注力するNXPは良い補完関係にある。

#STMicroelectronics to strengthen position in sensors with acquisition of NXP’s #MEMS sensors business.📎To read more: spkl.io/6013AHGKz

色々積み上げてきたオジサン達が挑戦するからこそカッコいいんですよ🥲

ラピダスの圧倒的オッサン&野郎しかいない感

ミニマルファブの動画、投稿し直しました✨ 貴重な実機映像が盛りだくさんです また見てくださると嬉しいです! ミニマルファブの現場へ潜入してきました! youtu.be/aAsSnN2JRxI?si… via @YouTube

Cadenceによると20/22nmでは、最小ピッチは80nm、7/10nmでは48nmとされます。 これらの数値は会社によって若干異なりますが、大きな差はありませんが、Intelの10nmは、TSMCの7nmとほぼ同等と言われます

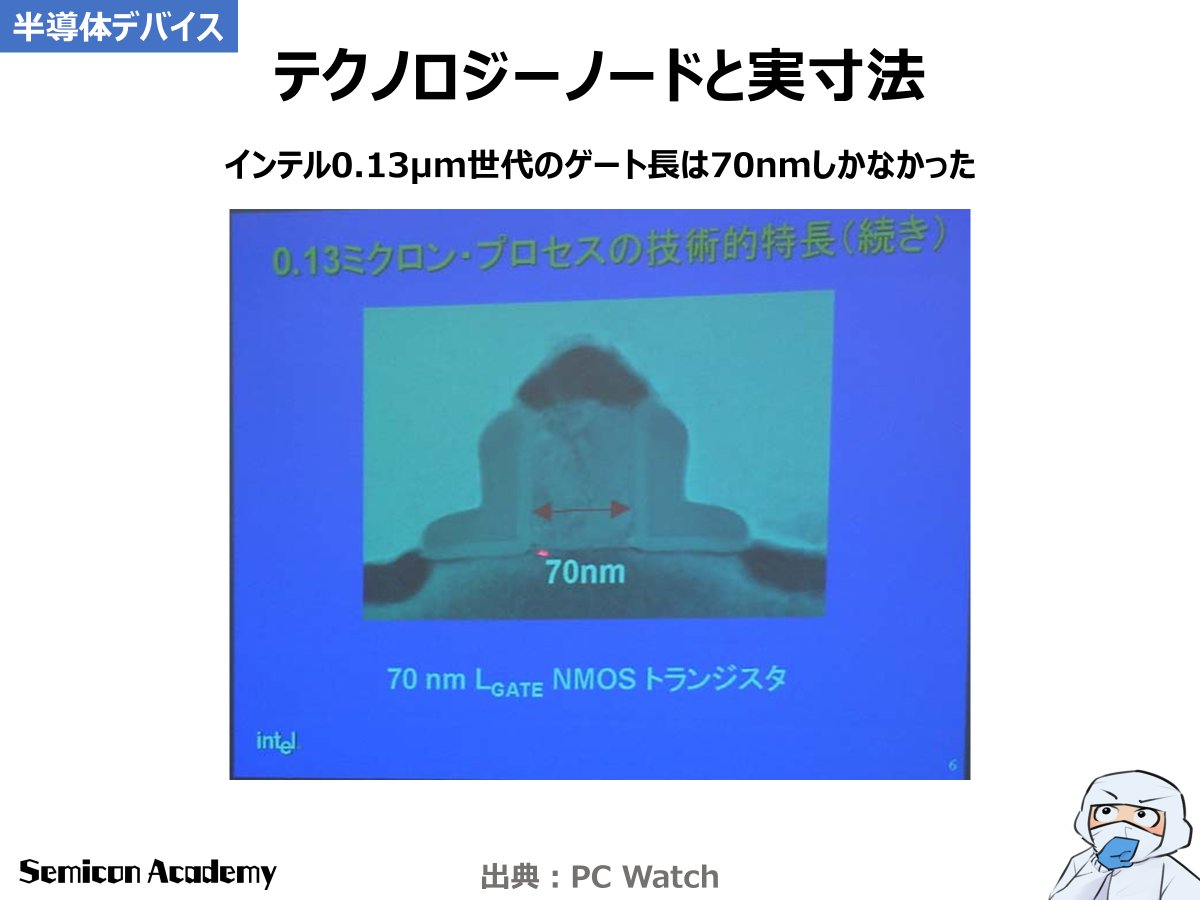

有名な話ですが、現代のテクノロジーノードはかつてのように実寸法を正確に反映していません。 2nmチップであってもメタル幅・ゲートピッチの実寸法は2nmよりずっと大きいです。 これと逆の現象も過去にあり、2001年に登場したintel 0.13μm世代のゲート長は、名称を下回る70nmしかありませんでした

なんだこのアカウントは!?

7月22日(火)に、ルネサスとの第5回目の団体交渉を行いました。今回の交渉では、ウルフスピードに関わる損失について、経営責任を問い質しました。

有名な話ですが、現代のテクノロジーノードはかつてのように実寸法を正確に反映していません。 2nmチップであってもメタル幅・ゲートピッチの実寸法は2nmよりずっと大きいです。 これと逆の現象も過去にあり、2001年に登場したintel 0.13μm世代のゲート長は、名称を下回る70nmしかありませんでした

ルネサス最終損益が1753億円で6年ぶり赤字 ウルフスピード破産による2350億円の損失計上がなければ黒なんですが、、、🥲 nikkei.com/article/DGXZQO…

最近公開されたロームの直販サイト、単価や在庫状況が見れるほか、少量発注にも対応しているので色々遊べそう ros.rohm.co.jp/category/%E3%8…

半導体クイズ回答編! ①LOCOS:Local Oxidation of Silicon ②STI:Shallow Trench Isolation LOCOSは半導体初期から使用されてきました。 しかし微細化が進むと分離特性劣化・閾値上昇などの問題に悩まされ、改良されていきます。 その後0.25μm世代からはSTIが本格的に導入されました #半導体クイズ

今週の半導体クイズ!! MOSFETなどのトランジスタが密に配置された状況では隣接する素子同士が干渉しないように、素子間を分離する構造が必要です。 ①の、シリコンを部分的に酸化させる手法 ②の、溝を掘って絶縁材料を埋め込む手法 それぞれ何と呼ぶでしょうか🧐 分野:デバイス 難易度:★★☆